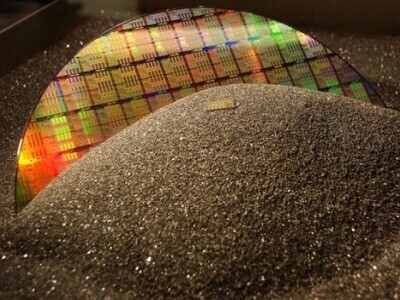

A TSMC az IEDM konferencián felvázolt egy útitervet, amelyben prezentálták, hogy milyen mértékű tranzisztorskálázásra lehet számítani az elkövetkező években.

A hagyományos, monolitikus felépítést tekintve az előrelépés visszafogott lesz, de ez nem meglepetés, mivel egy lapkára levetítve számos limitációval lehet szembesülni, ezek ráadásul esetenként nem kicsik. Ettől függetlenül 2030-ra reálisan elérhetővé vélik a 200 milliárd tranzisztor beépíthetősége egy komplex chip szintjén, ami megsüvegelendő, de a valóban erőteljes fejlődés a 3D-s tokozási technológiák által érhető majd tetten.

A mai komplex dizájnok már eleve ezeket használják, tehát a chiplet kialakítás elkerülhetetlen, a tokozás szempontjából pedig egyértelműen az az irány, hogy az egyes lapkák fizikailag egymásra kerüljenek. Az itt várható fejlesztéseket tekintve, az évtized végére elérhetővé válnak a legalább egybillió tranzisztort tartalmazó dizájnok. Persze itt főleg olyan termékekre kell majd gondolni, amelyek a szerverpiacra készülnek, tehát végfelhasználói szinten ez a komplexitás nehezen lesz megfizethető, de maga a 3D-s tokozás általánossá válthat a kliensekben is.